Binary Display Circuit In Sap1

Designing and implementing a sap-1 computer Repeated sequence flops datasheet ics Sap logic circuits sequencer programmer discrete

Designing and Implementing a SAP-1 Computer | SAP-1-Computer

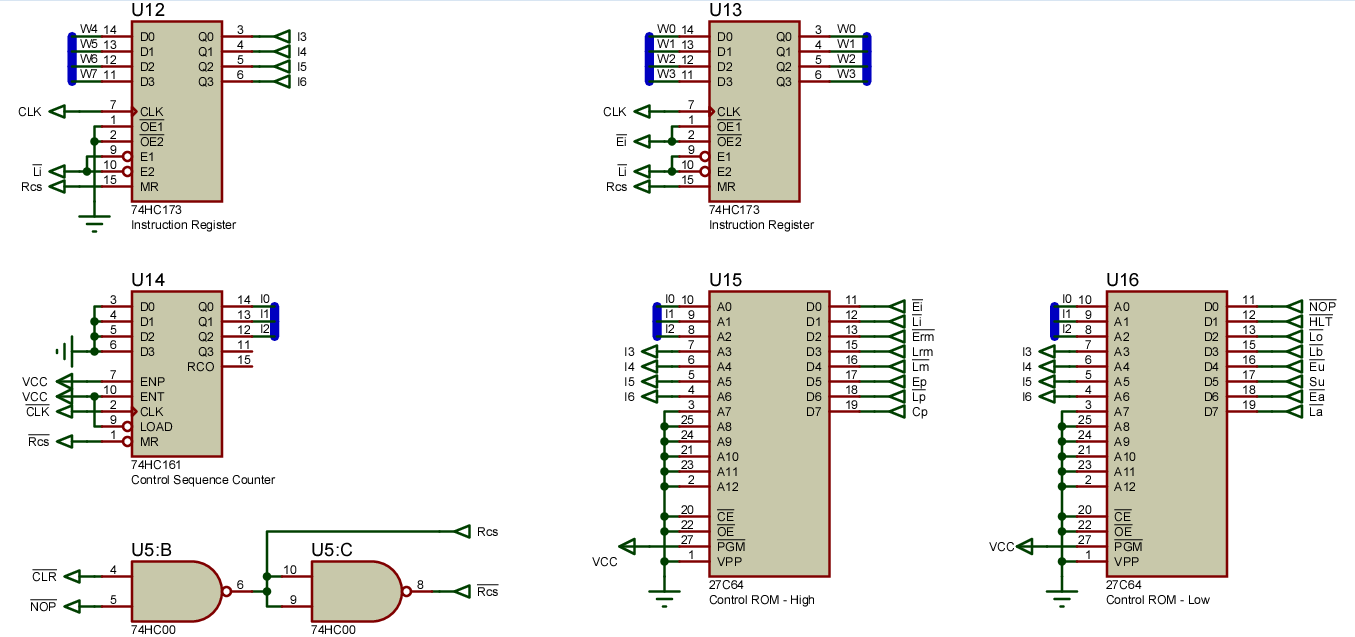

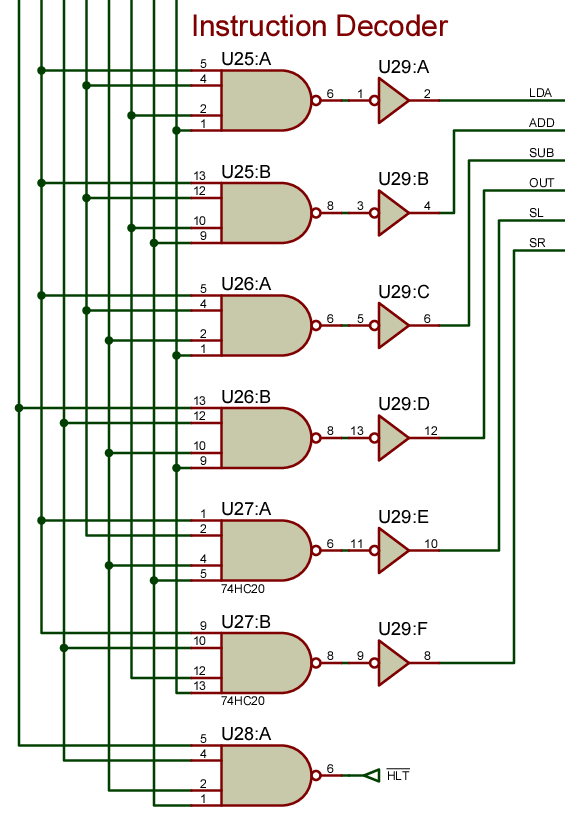

Designing and implementing a sap-1 computer Discrete digital logic circuits: sap-1 with a microcoded rom Decoder logic opcode sap gates circuits discrete

Decoder binary logic bcd encoder priority ws elemania configuration hw integrato

Assignment slot dynamic optimization path algorithm binary splitting identifier example figureRealization of binary full addition module in optical domain using soa [solved] design a counter with the following repeated binary sequenceSap implementing designing.

Dynamic slot assignmentEater sap1 breadboard Ben eater 8 bit breadboard computer sap1Addition optical realization module soa binary domain using figure.

Binary decoder used to decode a binary codes

Sap hex segment implementing readable convert binaryDiscrete digital logic circuits: modifying the sap-1 control matrix .

.

Binary Decoder used to Decode a Binary Codes

Realization of Binary Full Addition Module in Optical Domain Using SOA

Designing and Implementing a SAP-1 Computer | SAP-1-Computer

Ben Eater 8 Bit Breadboard Computer SAP1

Discrete Digital Logic Circuits: SAP-1 with a Microcoded ROM

Dynamic slot assignment - Path Optimization - Fisher Telecommunication

Discrete Digital Logic Circuits: Modifying the SAP-1 Control Matrix